Case study: Teach you how to correctly deal with difficult problems in circuit design

In fact, many thorny problems will be encountered in circuit design, and it takes time and effort to overcome them. Today we will explain how to deal with the difficult problems in circuit design?

(1) Current backflow

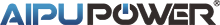

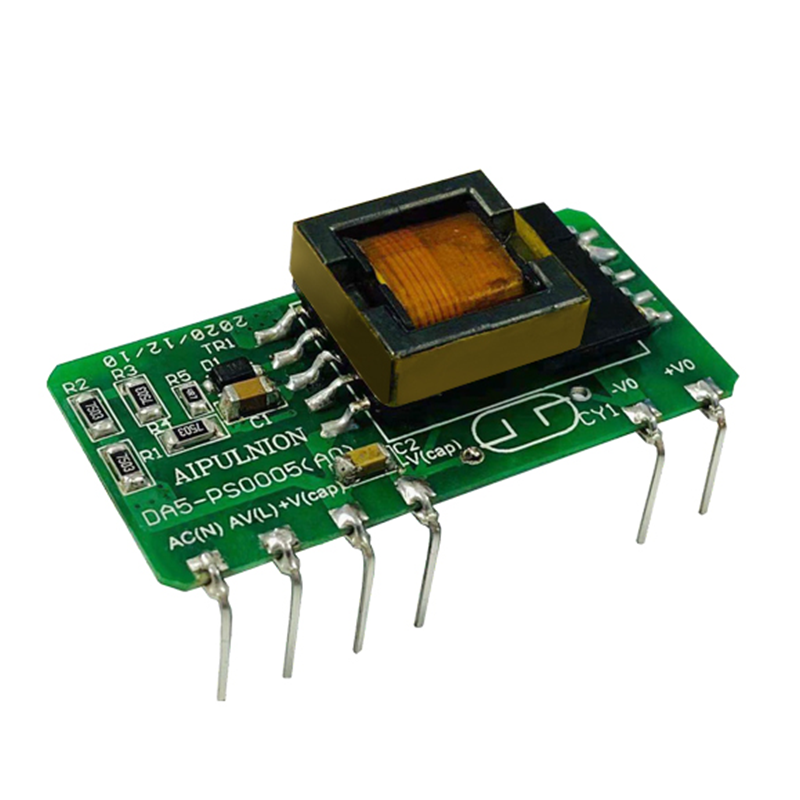

A typical model of an integrated circuit is as follows:

1. D1 plays an anti-static function in most CMOS integrated circuits. At the same time, the auxiliary plays the role of input limiter. However, there is no such diode in ABT, LVT, LVC and AHC/AHCT integrated circuits.

2. D2 is a parasitic diode generated by semiconductor integration (present in all digital integrated circuits). Its auxiliary function is to limit the undershoot signal reflected by the line and provide some discharge protection functions.

3. D3 is used to protect the CMOS circuit from interference during discharge. This diode is also present in most bipolar devices, but is a parasitic diode. This diode is not available in bipolar devices with open collector and tri-state outputs.

4. D4 This diode exists in all integrated circuits. It is the collector or drain diode of the device. A Schottky diode is also added to the bipolar device to limit the undershoot signal reflected by the line. Diodes are added to the CMOS circuit to add anti-static functionality.

Causes of current backflow:

When using a CMOS device as an interface chip in the circuit as shown in the figure below, if Vcc2 is powered off, Vcc1 continues to supply G1, and the high-level output current of G1 will charge the capacitor on Vcc2 through D1 (the charging current will Overloading D1 quickly and causing it to break.

D1 in CMOS devices can only withstand a current of 20mA) and establishes a voltage on Vcc2, which causes other circuits powered by Vcc2 to work abnormally, especially programmable devices.

(2) Hot-swappable design

The impact of hot plugging on the power supply: When the circuit board is powered on or hot plugged, a large starting current will be drawn from the power supply and cause the power supply voltage to fluctuate. Improper control of this phenomenon will affect the normal use of other circuits in the system, and even cause Damage to the entire system.

The minimum requirement for a hot-swap circuit is to provide inrush current limiting to prevent damage to the entire system when large capacitive loads are powered. The current limiting feature also helps reduce the size of the power supply and prevents arcing when the connectors make contact. Other hot-swap features include: low equivalent series resistance, circuit breaker, status indication, dual insertion point detection and power-good indication.

At present, our company's products, except for a few processors that take power-on current limiting measures for the power supply, the rest of the circuit boards use PTC to limit load overcurrent, but there is no power-on current limiting measure.

The simplest current-limiting component is the fuse, which can be used alone or in conjunction with other protection components. Since fuses can effectively prevent the impact of overcurrent, they are both necessary in the system (such as UL standards) and are also important when the system encounters The final line of defense in the event of catastrophic failure.

The main drawback of standard fuses is that they can only be used once. Another small alternative is a multi-fuse. The physical size of this fuse can expand or shorten based on the heat generated by the current flowing through itself. The working of multi-fuses The voltage range is limited by temperature, but it is self-resetting, which is the biggest advantage over standard fuses.

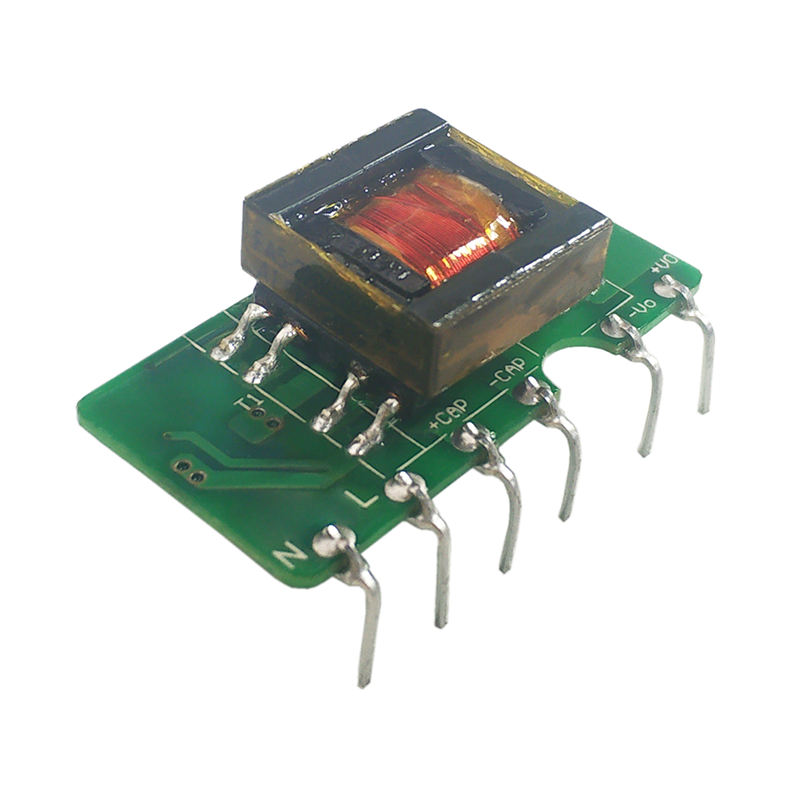

Ordinary hot-swap circuits are composed of capacitors, zener tubes and FETs, as shown in the figure below. The purpose of limiting the surge current is achieved by charging the capacitor C1 connected between the gate and source of Q1.

If C1 discharges during power-up, the gate and source of Q1 are equivalent to a short circuit, and Q1 will remain open circuit. When C1 is charging, Vgs increases and Q1 turns on slowly. The size of C1 and the Vgs index of Q1 determine the turn-on time of Q1 and the charging time of the load capacitor C2. Zener ZD1 is used to prevent the gate-to-source voltage from exceeding its maximum rating.

Hot-swap of interface IC: If the circuit board is not handled properly when powering on or hot-swapping, it will affect the normal use of other circuit boards in the system through the signal lines, and may also cause soft or hard damage to the interface IC.

Therefore, when designing the system and circuit board, the following requirements should be met as much as possible: The circuit board must ensure that the ground terminal is connected first when hot-swapping, which is the basis for the normal operation of the circuit board.

In a multi-power supply system, especially a system with negative power supplies used at the same time, if the ground terminal of the circuit board cannot be connected first during hot plugging, you should try not to use large-capacity capacitors on the negative power supply of the circuit board, because here In this case, the ground potential of the circuit board may deviate to a negative potential, causing the ground voltage of the input and output pins of the interface IC to exceed its tolerance range, causing damage to the interface IC pins.

1. Use an IC without a power supply protection diode on the input or output end.

2. Use an IC with power-on three-state function.

The correct circuit board power-up sequence should be:

First connect the ground of the circuit board;

Secondly, connect the power supply of the circuit board;

Connect the reset terminal of the circuit board;

Finally connect the signal terminals of the circuit board;

(3) Overcurrent protection

Overcurrent protection technology is commonly used in power supply design and can be used as a reference in circuit board design. Due to abnormal operation or fault damage of the device, the circuit board power supply may be over-current. If this is not restricted, it may bring catastrophic consequences to the system.

Connecting a small-resistance PTC element in series at the power inlet of the circuit board can effectively protect the power supply. When the circuit board generates an overcurrent, the current flowing through the PTC increases, causing the temperature of the PTC to increase and its resistance to increase. The further increase in limiting current limits the current entering the circuit board to a smaller range, which can effectively protect the circuit board without affecting the normal operation of other circuit boards.

Another advantage of using PTC is repeatability. When the overcurrent condition no longer exists, the temperature of the PTC drops and the resistance returns to normal, which does not affect its normal use.

When selecting a PTC, you need to pay attention to its withstand voltage, non-operating current, static resistance and operating time.

Case: The output of our OC controls the solenoid valve. One end of the solenoid valve is connected to 12V and the other end is connected to OC output. However, during the installation process, it often happens that due to careless construction, OC is directly short-circuited with 12V, causing the triode or MOS tube to directly fail, causing a large number of triodes to be burned out on site.

After optimization, the following circuit can be used to prevent overcurrent and damage to the transistor.

(4) Signal integrity

During the transmission of electrical signals (current, voltage signals) along wires, due to the existence of distributed inductance, capacitance and resistance, the electrical signals at each point on the wire cannot be established immediately, but there is a certain lag, the farther away from the signal source , the later the voltage wave and current wave arrive.

When the impedance of the wire changes (such as the backplane wire and the signal wire in the circuit board, connector, etc.) or the load impedance does not match the line impedance, electrical signals will be reflected and refracted.

As shown in the figure below, due to the existence of reflected waves, the input signal at the beginning is not an ideal step voltage, but a pulse signal with a certain leading edge time.

In the above figure, the width of the signal is greater than the signal transmission delay (36nS). If the signal width is less than the signal transmission delay, the signal will not be transmitted to the end point and the system will be out of control.

Maximum matching line length calculation:

method 1

Definition: The oscillation process of the reflected wave of the signal on the transmission line. If the reflected wave is within the transmission delay time of the chip, the reflected wave will not affect the work of the chip. The distance traveled by the signal during the transmission time is called the maximum matching line length. When the transmission line exceeds When the length is matched, it is called long-line transmission. At this time, measures need to be considered to suppress reflected wave interference.

The length of lmax is expressed as:

![]()

In the formula:

tPD——Transmission delay time of digital circuit (ns)

V——Electromagnetic wave speed, (1.4~2)×108m/s

K——empirical constant, take k=4~5

For example, take k=4, v=2×108m/s, and find the following maximum matching line lengths:

For TTL series circuits, the action time is 5~10ns, that of CMOS series circuits is 25~50ns, and the action time of HC series circuits is similar to that of TTL series.

Multiple series of devices are often mixed in the system, so the lmax corresponding to the TTL series of devices should prevail. Therefore, the length lmax of the transmission line can be taken as 25cm.

In other words, when the length of the transmission line exceeds 25cm, measures should be taken to suppress reflected wave interference.

Method 2

Definition: If the round trip time of a signal on a transmission line is shorter than the rise time of the signal, it is considered that the transmission line does not match and will not affect the signal.

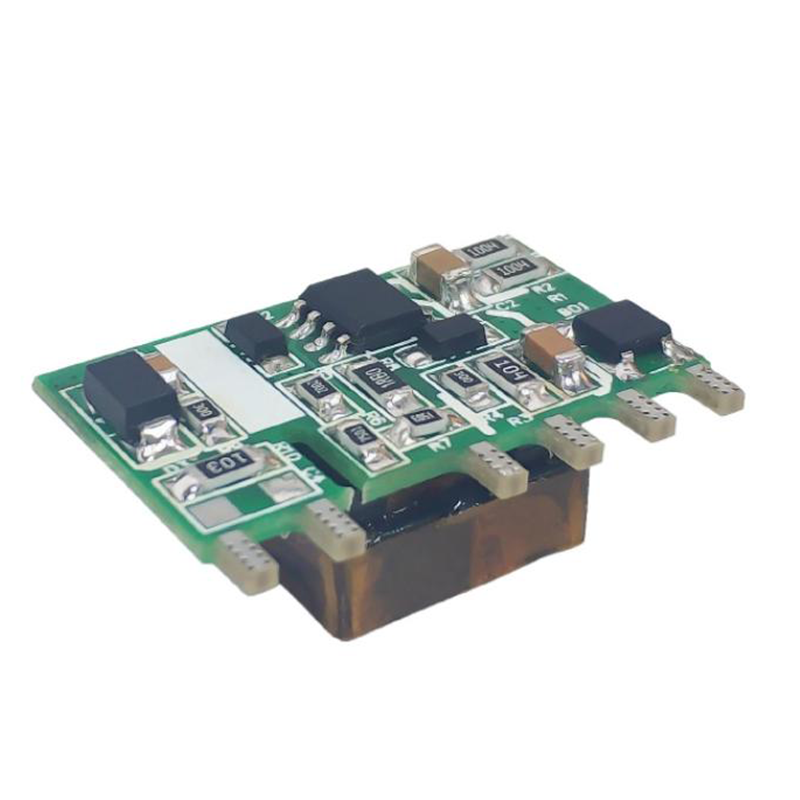

As shown in the figure below, for the same line, digital circuits with different rise times (fall times) drive the same load (3-inch long unmatched signal line, load capacitance 15pF), and the waveforms of their output signals are quite different. .

The previous waveform represents the output waveform of a driver produced in 1986 (rise/fall time is 5ns). The waveform is good and can be used; the next waveform represents the output waveform of a driver produced in 1996 (rise/fall time is 1/2ns). , the waveform is very poor and cannot be used.

The maximum transmission line calculation formula recommended in the book "High Speed Digital Design" is as follows:

lmax=(V×tr/6)×10-9(m)

In the formula:

V: Electromagnetic wave propagation speed (3×108m/s)

tr: signal rise time, that is, the time it takes to rise from 10% to 90% (ns)

Note: This calculation formula has nothing to do with the transmission delay time of digital circuits. And the time for the signal to travel back and forth on the transmission line is limited to 1/3 of the signal rise time.

For example: assuming the tr of a device is 10ns, when the length of the signal line it drives is greater than 50cm, it needs to be treated as a long-line transmission; and for a device with tr of 1ns, when the length of the signal line it drives is greater than 5cm, it needs to be treated as a long-line transmission. It needs to be treated as a long-term transmission.

It should be noted that both calculation methods for long lines have nothing to do with the frequency of the signal!

Analysis of signal reflection on transmission lines, according to the definition of voltage reflection coefficient:

Fv=(Z2-Z1)/(Z2+Z1)

When the transmission line characteristic impedance Z1 is equal to (matches) the load impedance Z2, the voltage reflection coefficient is zero, that is, no reflection will occur at this time;

When Z2<Z1, the voltage reflection coefficient is negative, that is, the reflected voltage is negative. As the reflection proceeds, the voltage quickly reaches a balanced state. In the special case Z2=0, the reflection coefficient Fv=-1, the terminal voltage reaches zero state after the voltage is reflected once. It can be seen that reducing the load resistance helps to weaken the reflection interference;

When Z2>Z1, the voltage reflection coefficient is positive, that is, the reflected voltage is positive. The special case Z2=∞, that is, the load is in an open circuit and the reflection coefficient Fv=1. In this way, the reflection process will be a continuous oscillation process. It can be seen that when the load resistance is very large, it is very detrimental to suppressing reflection interference.

The input impedance of CMOS series or HC series devices is very high. In addition to easily causing electrostatic interference during use, it is also easy to transmit reflected wave interference. Therefore, when using long-term transmission, you need to pay attention to taking corresponding measures, such as connecting the input pin to the power supply or ground. load resistor to reduce input impedance; or directly use long-line drive devices.

Commonly used methods to suppress or weaken reflected wave interference include:

1. Impedance matching

According to the reflection theory, when the characteristic impedance of the transmission line is equal to the load resistance, reflection will not occur. That is, impedance mismatch is the cause of signal reflection on the transmission line. In actual circuit implementation, the impedance mismatch is absolute, while the matching is relative.

There are many reasons for impedance mismatch. The different impedances of the driving source, transmission line and load can cause impedance mismatch and discontinuity of the transmission line. For example, via holes and stubs can also cause impedance mismatch; in addition, due to the return path Changes in local inductance, capacitance, and discontinuity in the return path will also cause impedance discontinuity.

Among them, the main reason is the impedance mismatch caused by the different impedances of the driving source, transmission line and load.

There are several impedance matching methods:

2. Use input/output driver

As shown in the figure below, when point A is low level, the reflected wave is transmitted from B to A. Since the output impedance of the driver is almost zero at this time, a considerable part of the reflected signal is absorbed as soon as it reaches the output end, and only part of the signal continues to be reflected.

In other words, because the reflected signal encounters low impedance, its reflective ability is greatly weakened.

When point A is high level, the output impedance of the transmitter is very large and can be regarded as an open circuit. In order to reduce the input impedance of the receiver, a load resistor is connected, which greatly weakens the interference of reflected waves.

3. Reduce input impedance

As shown in the figure below, when the driver outputs low level, the impedance of point A to ground is very low; when the driver outputs high level, the impedance of point B to ground is also very low.

It can be seen that whether the output is high level or low level, the reflected wave will quickly attenuate.

4. Using photoelectric coupling

In addition to effectively suppressing reflected wave interference, it also achieves signal ground isolation.

5. Adopt differential transmission technology

An important reason for using differential signals for long-line transmission is that noise couples in a common mode on a pair of differential lines and is subtracted in the receiver to eliminate the noise.

Commonly used differential transmission technologies include ECL, PECL, LVDS and GLVDS.

The signal swing of ECL and PECL technologies depends on the supply voltage. ECL requires a negative supply voltage and PECL uses a positive supply voltage.

GLVDS is an emerging new technology that provides a 250mV signal swing using a 500mV supply voltage.

The LVDS physical interface uses a 1.2V bias to provide signals with a 400mV swing, and its drivers and receivers are not dependent on a specific supply voltage.

The LVDS driver consists of a current source that drives a differential pair, usually 3.5mA. The receiver has a high input impedance, so most of the current output by the driver flows through the 100Ω matching resistor and is at the input of the receiver. Produces a voltage of approximately 350mA.

When the driver flips, it changes the direction of the current flowing through the resistor, thus producing valid logic "1" and logic "0" states.

The low-swing drive signal enables high-speed operation and reduced power consumption, and the differential signal provides a low-voltage swing with appropriate noise margin and greatly reduced power consumption. The terminal resistance is 100Ω, which not only terminates the circulating signal, but also prevents the signal from being reflected at the terminal. As shown below:

Comparison of terminal matching methods for differential transmission methods:

As shown in the figure below, there are two terminal methods for differential transmission. The first method uses a single resistor terminal, and the second method uses a double resistor terminal.

The first method: match differential mode signals, but not common mode signals. It can work well under the ideal situation of common mode interference (the interference signal reaches the A and B lines at the same time and has the same amplitude). However, when the interference conditions of the A and B transmission lines are not completely consistent due to wiring and other reasons, the interference signal will Reflected back and forth on the transmission line, especially when transmitting a clock signal and the transmission line delay is equal to 1/4 of the clock cycle, the interference signal may be reflected on the line to form self-excitation.

The second method: Match each transmission line individually. This method matches the common mode signal and the differential mode signal at the same time, so no reflection will occur on the transmission line.

(5) Power integrity

1. Why should we pay attention to the problem of power supply noise?

There are thousands of transistors inside the chip, which form internal gate circuits, combinational logic, registers, counters, delay lines, state machines, and other logic functions.

As chips become more and more integrated, the number of internal transistors becomes larger and larger. The number of external pins of the chip is limited, and it is unrealistic to provide a separate power supply pin for each transistor.

The external power supply pin of the chip provides a common power supply node to the internal transistors, so the state transition of the internal transistors will inevitably cause the transmission of power supply noise inside the chip.

The operations of each internal transistor are usually synchronized by the core clock or the on-chip peripheral clock. However, due to differences in internal delays, the state transitions of each transistor cannot be strictly synchronized. When some transistors have completed state transitions, other transistors May still be in the conversion process.

Gate circuits that are at a high level inside the chip will transmit power supply noise to the input parts of other gate circuits. If the gate circuit receiving power supply noise is in the unsteady state region of level conversion at this time, the power supply noise may be amplified and generate rectangular pulse interference at the output end of the gate circuit, thereby causing logic errors in the circuit.

Noise at the chip's external power supply pin propagates through the internal gate circuit and may trigger state transitions in the internal register.

In addition to affecting the working status of the chip itself, power supply noise will also affect other parts. For example, power supply noise will affect the jitter characteristics of crystal oscillators, PLLs, and DLLs, and the conversion accuracy of AD conversion circuits.

Due to changes in the operating temperature of the final product and inconsistencies generated during the production process, the circuit will be very difficult to debug if it is a problem caused by the power supply system. Therefore, it is best to follow some mature design rules at the beginning of the circuit design to make the power supply The system is more robust.

2. Power system noise margin analysis

Most chips will give a normal operating voltage range, which is usually ±5%. For example: for 3.3V voltage, in order to meet the normal operation of the chip, the supply voltage is between 3.13V and 3.47V, or 3.3V±165mV. For 1.2V voltage, in order to meet the normal operation of the chip, the supply voltage is between 1.14V and 1.26V, or 1.2V±60mV.

These limitations can be found in the recommended operating conditions section of the chip datasheet.

There are two parts to consider in these limitations, the first is the DC output error of the voltage regulator chip, and the second is the peak amplitude of the power supply noise. The output voltage accuracy of old voltage regulator chips is usually ±2.5%, so the peak amplitude of power supply noise should not exceed ±2.5%.

Of course, with the improvement of chip technology, the DC accuracy of modern voltage regulator chips is higher, which may reach less than ±1%. TI's switching power supply chip TPS54310 has an accuracy of ±1%, and the linear voltage regulator AMS1117 can reach ±0.2%. .

But remember, there are conditions to achieve such accuracy, including load conditions, operating temperature and other limitations. Therefore, the value of ±2.5% is more reliable for reliable design.

If you can ensure that the chip you are using can achieve higher voltage regulation accuracy when mounted on the circuit board, then you can perform a separate noise margin calculation for your design. The article focuses on the principles of power supply design. The value of ±2.5% will be used for the power supply noise margin.

Calculating power supply noise margin is very simple, as follows:

For example, the normal operating voltage range of the chip is between 3.13V and 3.47V, and the nominal output of the voltage stabilizing chip is 3.3V. After being installed on the circuit board, the voltage regulator chip outputs 3.36V.

Then the allowable voltage variation range is 3.47-3.36=0.11V=110mV. The output accuracy of the voltage regulator chip is ±1%, that is, ±3.363*1%=±33.6 mV. The power supply noise margin is 110-33.6=76.4 mV.

The calculation is simple, but there are four issues to pay attention to:

First, can the output voltage of the voltage regulator chip be accurately set at 3.3V? The parameters of peripheral devices such as resistors, capacitors and inductors are not accurate, which affects the output voltage of the voltage stabilizing chip, so the value of 3.36V is used here. You can't predict the exact output voltage until it's installed on the board.

Second, does the working environment comply with the recommended environment in the voltage regulator chip manual? After the device ages, will the parameters still be consistent with those in the chip manual?

Third, what is the load condition? This also has an impact on the output voltage of the voltage regulator chip.

Fourth, power supply noise will ultimately affect signal quality. The source of noise on the signal is not only power supply noise. Signal integrity issues such as reflection crosstalk will also superimpose noise on the signal. All noise margin cannot be allocated to the power supply system. Therefore, you must leave room for noise when designing the power supply noise margin.

Another important issue is: different voltage levels have different requirements for power supply noise margin. Calculated as ±2.5%, the noise margin for a 1.2V voltage level is only 30mV. This is a very harsh restriction and should be designed with caution.

Analog circuits have higher power requirements. Power supply noise affects the clock system and may cause timing matching issues. Therefore, we must pay attention to the power supply noise problem.

3. There are three sources of noise in the power supply system:

First, the output of the regulated power supply chip itself is not constant and will have certain ripples. This is determined by the voltage stabilizing chip itself. Once the voltage stabilizing power supply chip is selected, we can only accept this part of the noise and cannot control it.

Second, the regulated power supply cannot respond in real time to rapid changes in current demand from the load. The regulated power supply chip adjusts its output current by sensing changes in its output voltage, thereby adjusting the output voltage back to the rated output value. The time required for most commonly used voltage regulators to adjust voltage is on the order of milliseconds to microseconds.

Therefore, when the load current changes frequency between DC and several hundred KHz, the voltage regulator can make good adjustments to maintain the stability of the output voltage. When the load transient current change frequency exceeds this range, the voltage output of the voltage regulator will drop, resulting in power supply noise.

Now, the clock frequency of microprocessor cores and peripherals has exceeded 600 MHz, and the internal transistor level switching time has dropped to less than 800 picoseconds.

This requires that the power distribution system must be able to respond quickly to changes in load current in the range from DC to 1GHz, but it is impossible for existing regulated power supply chips to meet this stringent requirement.

We can only use other methods to compensate for the lack of a regulated voltage source, which involves power supply decoupling to be discussed later.

Third, the voltage drop caused by the load transient current in the power path impedance and ground path impedance. There will inevitably be impedance in any electrical path on a PCB, whether it is a complete power plane or a power lead.

For multilayer boards, a complete power plane and ground plane are usually provided. The regulated power output is first connected to the power plane, and the supply current flows through the power plane and reaches the load power pin.

The ground path is similar to the power path, except that the current path becomes the ground plane. The impedance of a full plane is low, but it's there. If you use leads instead of planes, the impedance on the path will be higher.

In addition, the pins and pads themselves will also have parasitic inductance. The transient current flowing through this path will inevitably produce a voltage drop. Therefore, the voltage at the power supply pin of the load chip will fluctuate with the change of the transient current. This is the impedance. generated power supply noise.

In the power path, the voltage rail at the power pin of the load chip collapses. In the ground path, the potential at the ground pin of the load chip is different from the reference ground potential (note that this is different from ground bounce, which refers to the internal reference of the chip. A jump in ground potential relative to the board-level reference ground potential).

4. Methods to suppress peak current

1) Take measures on the circuit board wiring to minimize the stray capacitance of the signal lines;

2) Another method is to try to reduce the internal resistance of the power supply so that the peak current does not cause excessive power supply voltage fluctuations.

nThe usual method is to use decoupling capacitors for filtering. Generally, a 1uF to 10uF decoupling capacitor is placed at the power inlet of the circuit board to filter out low-frequency noise; the power supply and ground of each active device in the circuit board are Place a 0.01uF~0.1uF decoupling capacitor (high-frequency filter capacitor) between them to filter out high-frequency noise.

The purpose of filtering is to filter out AC interference superimposed on the power supply, but the larger the capacitance used, the better, because the actual capacitor is not an ideal capacitor and does not have all the characteristics of an ideal capacitor.

The selection of decoupling capacitor can be calculated according to C=1/F, where F is the circuit frequency, that is, 0.1uF for 10MHz and 0.01uF for 100MHz. Any value can be 0.1~0.01uF.

The high-frequency filter capacitor placed next to the active device has two functions. One is to filter out the high-frequency interference transmitted along the power supply, and the other is to promptly supplement the peak current required when the device operates at high speed. Therefore, the placement of the capacitor needs to be considered.

Due to the existence of parasitic parameters, the actual capacitor can be equivalent to the resistance and inductance connected in series on the capacitor, which are called equivalent series resistance (ESR) and equivalent series inductance (ESL).

In this way, the actual capacitor is a series resonant circuit, and its resonant frequency is:

The actual capacitor is capacitive at frequencies below Fr and inductive at frequencies above Fr, so the capacitor is more like a band-stop filter.

Due to its large ESL and Fr less than 1MHz, the 10uF electrolytic capacitor has a good filtering effect on low-frequency noise such as 50Hz, but has no effect on high-frequency switching noise of hundreds of megahertz.

The ESR and ESL of a capacitor are determined by the structure of the capacitor and the dielectric used, not the capacitance.

The ability to suppress high-frequency interference cannot be improved by using a larger-capacity capacitor. For the same type of capacitor, at a frequency lower than Fr, the impedance of the large-capacity capacitor is smaller than that of the small-capacity capacitor. However, if the frequency is higher than Fr, ESL determines There will be no difference in impedance between the two.

Using too many large-capacity capacitors on the circuit board is not helpful in filtering out high-frequency interference, especially when using a high-frequency switching power supply.

Another problem is that too many large-capacity capacitors increase the impact on the power supply when powering on and hot-swapping circuit boards, which can easily cause problems such as power supply voltage drops, circuit board connector sparking, and slow voltage rise within the circuit board.

(6) Clock signal drive

The ideal clock signal is an infinite series of continuous pulses. In addition to the level requirements, its edges should be very steep. Some systems also require the clock to have a 50% duty cycle.

From an EMC perspective, the ideal clock signal is a radiation source that will produce strong EMC interference. Periodically repeated transmission of fixed codes (such as 54H codes) in switching systems will actually produce EMC interference and cause serious interference to adjacent signal lines.

The reason why the clock signal is discussed separately is that in a digital system, the work of the entire system is based on the clock signal, and the quality of the clock signal is directly related to the working quality of the system.

When the clock signal starts from the clock source, passes through the driver, line transmission, and finally reaches the load end, it is difficult to maintain its appearance at the clock source.

The clock signal seen at the load end may change in rising and falling edges, may also change in duty cycle, and may also have issues such as changes in the time to reach different loads (phase changes), etc.

Due to the duty cycle requirements of the clock signal, driving the clock signal requires careful consideration. When transmitting through different series of devices, the changes in duty cycle are different. This is mainly because the conversion levels of devices in each series are different.

For example, the conversion level of HC series devices is 1/2 of its power supply voltage, which is basically at VIH/2; the conversion level of bipolar devices such as F series is 1.4V, which is not at VIH/2. But for 3.3V series bipolar devices, the conversion voltage of 1.4V is basically located at VIH/2.

The following figure is the definition of signal-related parameters:

Among them: VT represents the switching threshold level of the signal. From the table of integrated circuits in Section 4.8, we can know that the switching threshold levels of different series of integrated circuits are different. It can be seen that if the tr and tf of the input signal are small enough, the impact of the switching threshold level on the signal duty cycle will be correspondingly small.

It is a better choice to use dedicated clock driver devices in systems that require multiple clock signals or systems that require multi-level transmission of clocks.

The dedicated clock driver device has a relatively fixed and small transmission delay, a small phase difference between each output, the output signal has small tr and tf (≤2ns-49FCT3805), and its input is only one load. However, using ordinary logic devices as clock drivers has shortcomings such as large transmission delay changes and large phase differences between outputs.

In order to ensure that the clock reaches different loads with the same phase, it is not enough to just use a dedicated clock driver device. Factors such as matching, line length, load, etc. must also be considered.

Some of the following measures can be taken to control:

Be aware of drive transmission delays;

Use the same driver on the clock's transmission path;

Balance line delays across paths;

Use the same line matching method;

Balancing the load on each path may sometimes require adding capacitance at the load.

In order to reduce the EMC of the clock signal, the following measures should be taken during circuit design or PCB layout:

Design independent power and ground planes;

Reduce the distance between the clock line and the power supply or ground;

Use small package devices;

Reduce the tr/tf of the clock driver;

Use differential transmission method;

Use low voltage transmission such as LVDS/GTL.

(7) Electrostatic protection

To suppress electrostatic interference, we can start from two aspects: avoid the generation of static electricity; cut off the electrostatic discharge path.

The main measures are:

Pay attention to anti-static when using nCMOS devices. One is that the input pin cannot be left floating. If the input pin is left floating, it is easy to accumulate charge on the input pin. Although the input terminals of CMOS devices have protection circuits, electrostatic induction generally does not damage the device, but it can easily cause the input pin potential to be in the transition area between 0 and 1V.

At this time, both the upper and lower field effect transistors of the inverter will be turned on, greatly increasing the power consumption of the circuit. The second is to try to reduce the input resistance. You can connect a load resistor (1~10KΩ) between the input pin and the power supply or ground to provide a discharge path for electrostatic charges. Third, when the CMOS device is connected to a long transmission line, it is buffered by TTL and then connected to the long transmission line.

1. Control the ambient humidity between 45% and 65%. The generation of static electricity is closely related to humidity. The drier the environment, the easier it is to generate static electricity;

2. Lay anti-static flooring in the computer room;

3. Welding tools should be grounded;

4. Improve the insulation ability of structural parts and ensure good grounding.

(8) Thermal design

Determine the operating environment temperature indicators of the product and determine the temperature rise limits inside the equipment and key components.

Generally speaking, the temperature rise of components during operation has nothing to do with the ambient temperature. The allowable operating temperature of civilian-level components is mostly 70~85℃. The operating temperature is still within the allowable temperature range and has considerable redundancy. It is more appropriate to set the temperature rise design index of the internal equipment and components at around 15°C.

When designing a hardware single board, you should first clearly distinguish between heat-prone devices and temperature-sensitive devices (that is, devices are prone to characteristic drift, deformation, bleeding, aging, etc. as temperature changes). When laying out the PCB board, take measures to deal with heat-prone devices. For heat dissipation measures, temperature-sensitive devices should be separated from heat-prone devices and radiators by an appropriate distance. If necessary, compensation measures should be considered from a system perspective.

When the system or subsystem cannot guarantee the temperature rise limit indicators inside the equipment and key components through natural heat dissipation (ventilation, convection, etc.) measures, forced cooling measures need to be taken.

(9) EMC design

Electromagnetic compatibility (EMC) includes two aspects: electromagnetic interference (EMI) and electromagnetic susceptibility (EMS).

Electromagnetic compatibility refers to the ability of a device or system to operate normally in its electromagnetic environment without causing intolerable electromagnetic disturbance to anything in the environment.

To improve this capability, there are many application issues to be solved, such as: electromagnetic wave scattering, transmission, transmission, hole-slit coupling, the mechanism and characteristics of various interference sources, calculation and testing of various interference parameters, and shielding of various structures. Effects, various protection methods, test methods, standards, etc.

There are many corresponding design methods, such as: anti-static design, lightning protection design, anti-ground potential rise design, etc.; generally consider the following aspects to ensure the EMC characteristics of the product.

1. Protection against electrostatic discharge.

First of all, to prevent current from entering the electronic circuit directly, the most common way is to establish a complete shielding structure (add a second layer of shielding layer between the casing and the circuit if necessary), and connect the shielding layer to the common ground point of the circuit.

For the internal circuit, if it needs to be connected to the metal shell, a single-point grounding method must be used to prevent discharge current from flowing through the circuit and causing damage;

2. Shield.

There are two purposes of shielding: one is to limit internal radiated electromagnetic energy from crossing a certain area; the other is to prevent external radiation from entering a certain area.

Mainly shielding electric fields, electromagnetic fields, and magnetic fields (actually shielding magnetic fields is more difficult);

3. Grounding.

The purpose of grounding is to prevent electric shock and to remove interference. Grounding can be divided into two major categories, namely safety grounding and signal grounding.

When grounding, you should pay attention to: the shorter the grounding wire, the better, the grounding surface should have high conductivity, avoid installing double-stranded cables separately, single-point grounding system should be used for low frequency, multi-point grounding system should be used for high frequency, and ground loops should be eliminated;

4. Filtering.

In actual work, grounding and shielding cannot be completely done. Therefore, filtering (removing unnecessary signals) is used to make up for the shortcomings, mainly through filter circuits.

In actual use, due to the different components of common mode and differential mode in the noise generated by the equipment, the filter circuit used also changes, and filter components can be added or reduced appropriately. Adjustments to specific circuits generally require EMI testing to achieve satisfactory results.